作者:河南的小人物 | 来源:互联网 | 2023-10-10 16:13

篇首语:本文由编程笔记#小编为大家整理,主要介绍了存储器层次结构相关的知识,希望对你有一定的参考价值。

实际的软件开发过程中,常会遇到服务端请求响应时间长,吞吐率不够。

分析对应问题时,你肯定听过“主要瓶颈不在CPU,而在I/O”,存储很重要。

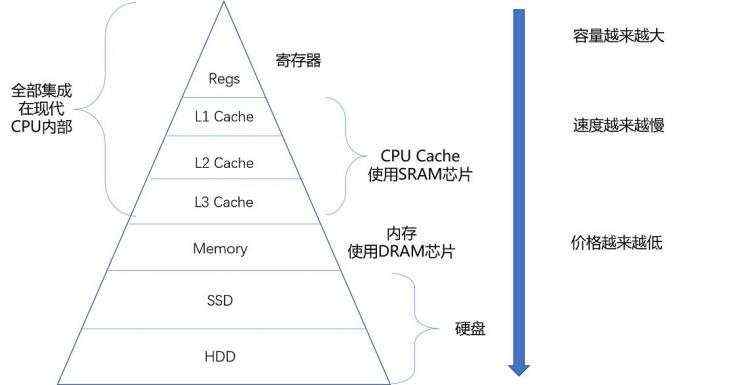

1 存储器的层次结构

存储器系统是通过各种不同方法和设备,一层层组合起来的系统。

常把CPU比做计算机的“大脑”,思考的东西,好比CPU的寄存器(Register)。寄存器与其说是存储器,更像是CPU本身一部分,只能存放极有限信息,但速度很快,和CPU同步。

大脑中的记忆好比CPU Cache(CPU高速缓存,简称为“缓存”)。CPU Cache用的一种SRAM(Static Random-Access Memory,静态随机存取存储器)芯片。

2 SRAM

“静态”,因为只要处在通电状态,里面数据就能保持存在。一旦断电,里面数据就丢失。

SRAM里,一个比特数据,需6~8个晶体管。所以SRAM存储密度不高。同样物理空间下,能存储数据有限。但SRAM电路简单,所以访问速度很快。

6个晶体管组成SRAM的一个比特:

CPU里通常有L1、L2、L3三层高速缓存。

每个CPU核心都有一块属于自己的L1高速缓存,通常分成:

- 指令缓存

存放CPU使用的指令 - 数据缓存

存放CPU使用的数据

这里的指令缓存和数据缓存,就来自哈佛架构。

把内存当成我们拥有的书架。当我们记忆中没有资料时,可从书架拿书翻阅。这过程相当于,数据从内存中加载到CPU的寄存器和Cache中,然后通过“大脑”(CPU),进行处理和运算。

3 DRAM

内存用的DRAM(Dynamic Random Access Memory,动态随机存取存储器)芯片,比SRAM密度更高,有更大容量,比SRAM芯片便宜。

“动态”,因为需靠不断“刷新”,才能保持数据被存储。DRAM的一个比特,只需一个晶体管、一个电容就能存储。所以,DRAM在同样物理空间下,能存储数据更多,即存储“密度”更大。但数据存在电容,电容会不断漏电,所以需定时刷新充电,才能保持数据不丢失。DRAM的数据访问电路和刷新电路都比SRAM更复杂,访问延时更长。

4 存储器的层级结构

整个存储器的层次结构都类似SRAM和DRAM在性能、价格差异:

-

SRAM更贵,速度更快

像大脑中的记忆

-

DRAM更便宜,容量更大

像属于我们自己的书桌

大脑(CPU)中的记忆(L1 Cache),不仅受成本限制,更受物理限制,好比L1 Cache不仅昂贵,其访问速度和它到CPU的物理距离有关。芯片越大,总有部分离CPU的距离会变远。电信号的传输速度又受物理限制,没法超过光速。所以想要快,并非靠多花钱就能解决。

书房(即内存)空间有限,无法放下所有书(即数据)。若想扩大空间,相当于要多买几平方房子,成本很高。于是,想要放下更多书,就要寻找廉价方案。即公共图书馆,对内存来说:

- SSD(Solid-state drive或Solid-state disk,固态硬盘)

- HDD(Hard Disk Drive,硬盘)

这些被称为硬盘的外部存储设备,即公共图书馆。于是,就可去家附近图书馆借书。图书馆有更多空间(存储空间)和更多书(数据)。

而HDD则是一种完全符合“磁盘”名字的传统硬件。“磁盘”硬件结构决定它的访问速度受限于物理结构,最慢。

存储器层次关系图

从Cache、内存,到SSD和HDD硬盘。容量越小的设备速度越快,而且,CPU并不是直接和每一种存储器设备打交道,而是每一种存储器设备,只和它相邻的存储设备打交道。比如,CPU Cache是从内存里加载而来的,或者需要写回内存,并不会直接写回数据到硬盘,也不会直接从硬盘加载数据到CPU Cache中,而是先加载到内存,再从内存加载到Cache中。

这样,各个存储器只和相邻的一层存储器打交道,并且随着一层层向下,存储器的容量逐层增大,访问速度逐层变慢,而单位存储成本也逐层下降,也就构成了我们日常所说的存储器层次结构。

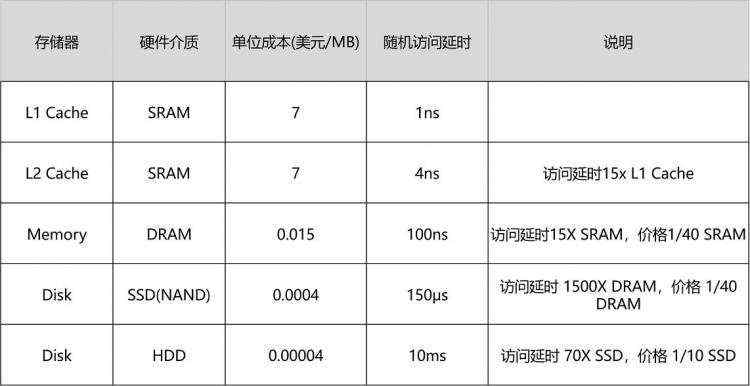

5 权衡价格和性能?

存储器在不同层级之间的性能差异和价格差异,都至少在一个数量级以上。L1 Cache的访问延时是1纳秒(ns),而内存就已经是100纳秒了。在价格上,这两者也差出了400倍。

各种存储器成本的对比表格

实际在进行电脑硬件配置的时候,会去组合配置各种存储设备。

如,一款入门级的惠普战66的笔记本电脑。今天在京东上的价格是4999人民币

Intle i5-8265U的CPU(这是一块4核的CPU)

这块CPU每个核有32KB,一共128KB的L1指令Cache。

同样,每个核还有32KB,一共128KB的L1数据Cache,指令Cache和数据Cache都是采用8路组相连的放置策略。

每个核有256KB,一共1MB的L2 Cache。L2 Cache是用4路组相连的放置策略。

最后还有一块多个核心共用的12MB的L3 Cache,采用的是12路组相连的放置策略。

8GB的内存

一块128G的SSD硬盘

一块1T的HDD硬盘

一台实际的计算机里面,越是速度快的设备,容量就越小。这里一共十多兆的Cache,成本只是几十美元。而8GB的内存、128G的SSD以及1T的HDD,大概零售价格加在一起,也就和我们的高速缓存的价格差不多。

6 总结

CPU比喻成高速运转的大脑,和大脑同步的寄存器(Register),就存放着当下正在思考和处理的数据。

L1-L3的CPU Cache,好比存放在我们大脑中的短期到长期的记忆。需要小小花费一点时间,就能调取并进行处理。

书桌书架就好比计算机的内存,能放下更多的书也就是数据,但是找起来和看起来就要慢上不少。

而图书馆更像硬盘这个外存,能够放下更多的数据,找起来也更费时间。

从寄存器、CPU Cache,到内存、硬盘,这样一层层下来的存储器,速度越来越慢,空间越来越大,价格也越来越便宜。

这三个“越来越”的特性,使得我们在组装计算机的时候,要组合使用各种存储设备。越是快且贵的设备,实际在一台计算机里面的存储空间往往就越小。而越是慢且便宜的设备,在实际组装的计算机里面的存储空间就会越大。

参考

- Peter Novig的Teach Yourself Programming in Ten Years,这些数字随着摩尔定律的发展在不断缩小,但是在数量级上仍然有着很强的参考价值。

- Jeff Dean的Build Software Systems at Google and Lessons Learned。这份PPT中不仅总结了这些数字,还有大量的硬件故障、高可用和系统架构的血泪经验。